### Reflections on a career in

## Semiconductors and Academia

Mark Lundstrom

December 12, 2025

### The two strands of my career

| 1969                                 | Freshman at the University of Minneso                                                                                                               | ota |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1973<br>1974<br>1975                 | BEE MSEE IC process development and manufact                                                                                                        |     |

| 1977<br>1980<br>1991<br>1994<br>2005 | Began PhD at Purdue Joined Purdue faculty Got a taste of administration Decided I was meant to be a professor Decided to finish my career at Purdue |     |

| 2020<br>2021<br>2022                 | Acting Dean of Engineering Principal Advisor to the EVPSI Interim Dean                                                                              |     |

**Chief Semiconductor Officer**

2023

# "The greatest moment since mankind emerged as a

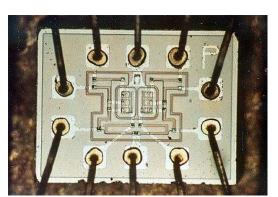

Vacuum tube 1904

**Transistor** 1947, 1960

Silicon chip 1960

## The two strands of my career

| 1969<br>1973<br>1974<br>1975 | Freshman at the University of Minnesota<br>BEE<br>MSEE<br>IC process development and manufacturing |

|------------------------------|----------------------------------------------------------------------------------------------------|

| 1977<br>1980                 | Began PhD at Purdue Joined Purdue faculty                                                          |

| 1991                         | Got a taste of administration                                                                      |

| 1994                         | Decided I was meant to be a professor                                                              |

| 2005                         | Decided to finish my career at Purdue                                                              |

| 2020                         | Acting Dean of Engineering                                                                         |

|                              |                                                                                                    |

| 2021                         | Principle Advisor to the EVPSI                                                                     |

| 2021<br>2022                 | Principle Advisor to the EVPSI Interim Dean                                                        |

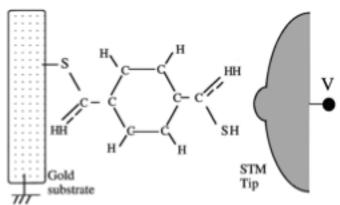

#### Molecular electronics (late 1990's)

**Professor Supriyo Datta**

VOLUME 79, NUMBER 13

PHYSICAL REVIEW LETTERS

29 September 1997

#### Current-Voltage Characteristics of Self-Assembled Monolayers by Scanning Tunneling Microscopy

Supriyo Datta and Weidong Tian

School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907-1285

Seunghun Hong and R. Reifenberger

Department of Physics, Purdue University, West Lafayette, Indiana 47907-1285

Jason I. Henderson and Clifford P. Kubiak

Department of Chemistry, Purdue University, West Lafayette, Indiana 47907-1285 (Received 9 June 1997)

This paper presents a comparison of the theoretical and experimental current-voltage (I-V) characteristics of a self-assembled monolayer of  $\alpha$ ,  $\alpha'$ -xylyl dithiol molecules on a gold substrate measured with a scanning tunneling microscope probe. Good quantitative agreement is obtained with the tip-molecule distance as the only "fitting parameter." Several other thiol-coupled molecules that we have studied also show similar agreement. The conceptual picture presented in this paper could be useful for the interpretation of I-V measurements on molecular monolayers in general. [S0031-9007(97)04094-5]

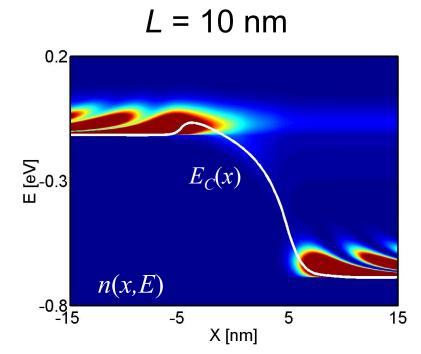

#### Computational electronics at the atomic scale

Position along channel (nm)

Ren, Venugopal, Goasguen, Datta, and Lundstrom, TED, **50**, p. 2185, 2003.

Abstract—A simple one-flux scattering theory of the silicon MOSFET is introduced. Current-voltage (I-V) characteristics are expressed in terms of scattering parameters rather than a mobility. For long-channel transistors, the results reduce to conventional drift-diffusion theory, but they also apply to devices in which the channel length is comparable to or even shorter than the mean-free-path. The results indicate that for very short channels the transconductance is limited by carrier injection from the source. The theory also indicates that evaluation of the drain current in short-channel MOSFET's is a near-equilibrium transport problem, even though the channel electric field is large in magnitude and varies rapidly in space.

CHANNEL lengths and supply voltages of MOSFET's are saturated drain current  $I_{D_{\rm SML}}$  for short-channel, low-voltage devices. Identifying the limiting value of  $I_{D_{\rm SML}}$  as L approach zero and understanding the role of velocity overshoot are important issues that have been examined experimentally and theoretically [1]–[4]. This letter presents a simple scattering model for  $I_{D_{\rm SML}}$  which should be useful for interpreting detailed simulations and for guiding device design.

$$I_{Dsat} = C_{ox}W \upsilon_T \left(\frac{1-r_c}{1+r_c}\right) (V_{GS} - V_T)$$

APPLIED PHYSICS

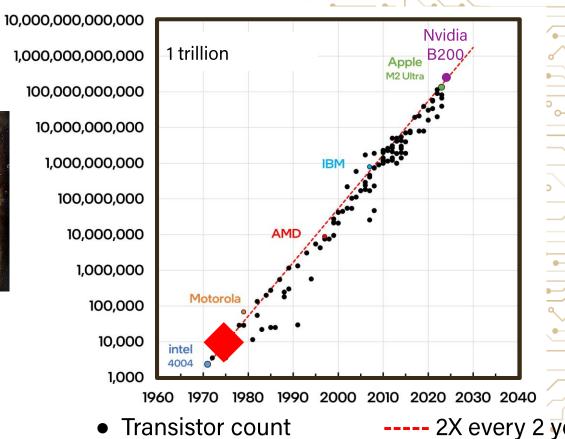

#### Moore's Law Forever?

**Mark Lundstrom**

hen Gordon Moore predicted in 1965 that the number of transistors per integrated circuit chip would continue to double in each technology generation, there were just 30 transis-

Enhanced online at www.sciencemag.org/cgi/ content/full/299/5604/210

www.sciencemag.org/cgi/ content/full/299/5604/210 counts—a measure of the capability of an electronic system—exceed a few hundred million for logic chips and even more for memory chips. How long can Moore's law continue?

The semiconductor industry follows Moore's law by shrinking transistor dimensions. But transistors cannot be scaled down infinitely. A few years ago, as critical dimensions approached 100 nm, a number of formidable challenges arose (1). It seemed that progress would slow, but during the past few years, device scaling has accelerated, as evidenced by several talks at the recent International Electron Devices Meeting (IEDM) (2).

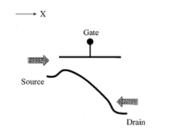

Today's electronic devices are based on the metal oxide semiconductor field-effect transistor (MOSFET), which consists of source and drain electrodes, through which current can flow, and a gate electrode, which controls the current through the other two (see the figure). MOSFETs operate on a simple principle: When the gate voltage is low, an energy barrier prevents electrons from flowing from source to drain, whereas a high gate voltage lowers the energy barrier, allowing current to flow (see the figure). The gate electrode is separated from the silicon channel by a thin insulating layer to prevent the flow of gate current.

To comply with Moore's law, the transistor designer must shrink the distance between source and drain by a factor of  $\sqrt{2}$  in each technology generation. This reduces the area by a factor of 2, thereby doubling the number of transistors per chip. Remarkable advances in subwavelength lithography allow current-generation technologies with gate lengths of 65 nm to be

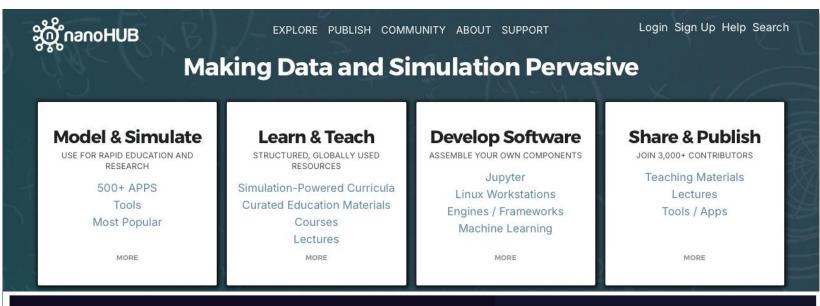

### nanoHUB.org – 30 years and still going strong

### The two strands of my career

Technology

| 1969<br>1973<br>1974<br>1975                | Freshman at the University of Minnesota<br>BEE<br>MSEE<br>IC process development and manufacturi                                                    |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1977<br>1980<br>1991<br>1994<br><b>2005</b> | Began PhD at Purdue Joined Purdue faculty Got a taste of administration Decided I was meant to be a professor Decided to finish my career at Purdue |

| 2020<br>2021<br>2022                        | Acting Dean of Engineering Principal Advisor to the EVPSI Interim Dean                                                                              |

**Chief Semiconductor Officer**

2023

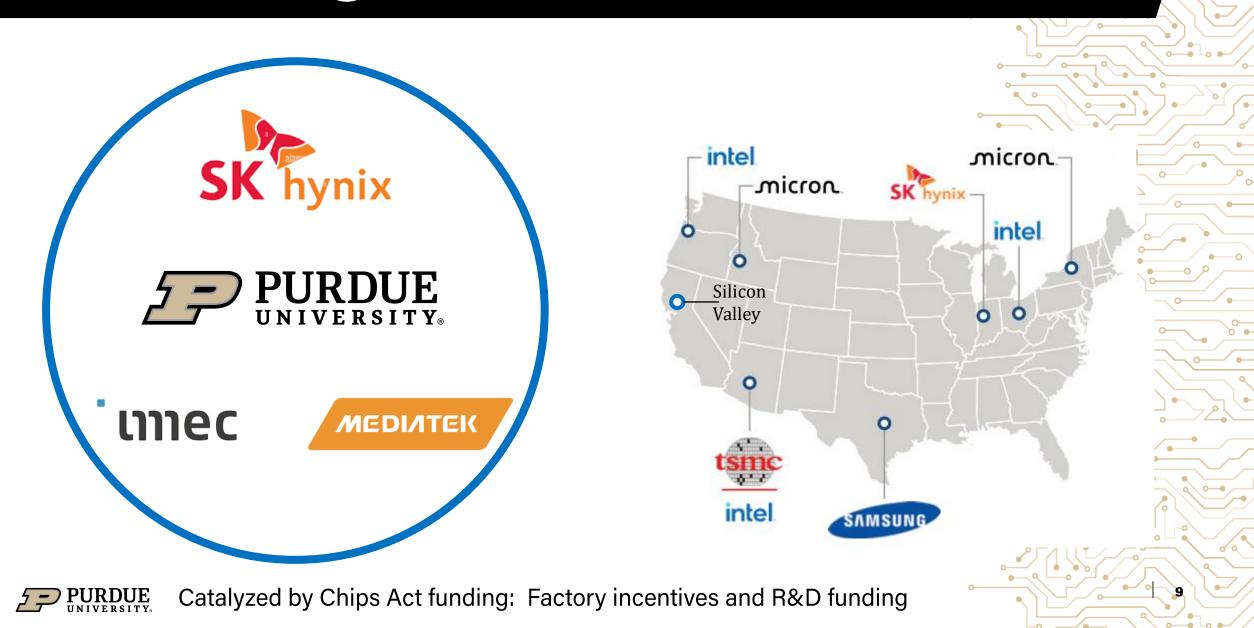

#### Semiconductors@Purdue...

### Looking back...

| 1969 | Freshman at the University of Minnesota  |

|------|------------------------------------------|

| 1973 | BEE                                      |

| 1974 | MSEE                                     |

| 1975 | IC process development and manufacturing |

|      |                                          |

| 1977 | Began PhD at Purdue                      |

| 1980 | Joined Purdue faculty                    |

| 1991 | Got a taste of administration            |

| 1994 | Decided I was meant to be a professor    |

| 2005 | Decided to finish my career at Purdue    |

|      |                                          |

| 2020 | Acting Dean of Engineering               |

| 2021 | Principal Advisor to the EVPSI           |

| 2022 | Interim Dean                             |

| 2023 | Chief Semiconductor Officer              |

**Professor Emeritus**

????